台积公司举办在线技术论坛及开放创新平台生态系统论坛揭示最新先进技术

作者:单祥茹 来源:中国电子商情

发布时间:2020-08-25

2020年8月25日,台积公司(TSMC)首度举办在线技术论坛及开放创新平台(Open Innovation Platform, OIP®)生态系统论坛,会中揭示先进逻辑技术、特殊技术、三维集成电路(3DIC)系统整合解决方案,以及其完备设计实现生态系统的最新发展。新冠肺炎疫情期间,台积公司采用在线形式进行此年度最盛大的论坛活动,与客户及生态系统伙伴们维持重要且密切的连系。来自231家公司,共计超过750位专业人士注册参与8月25日在中国大陆举行的在线技术论坛及开放创新平台生态系统论坛。

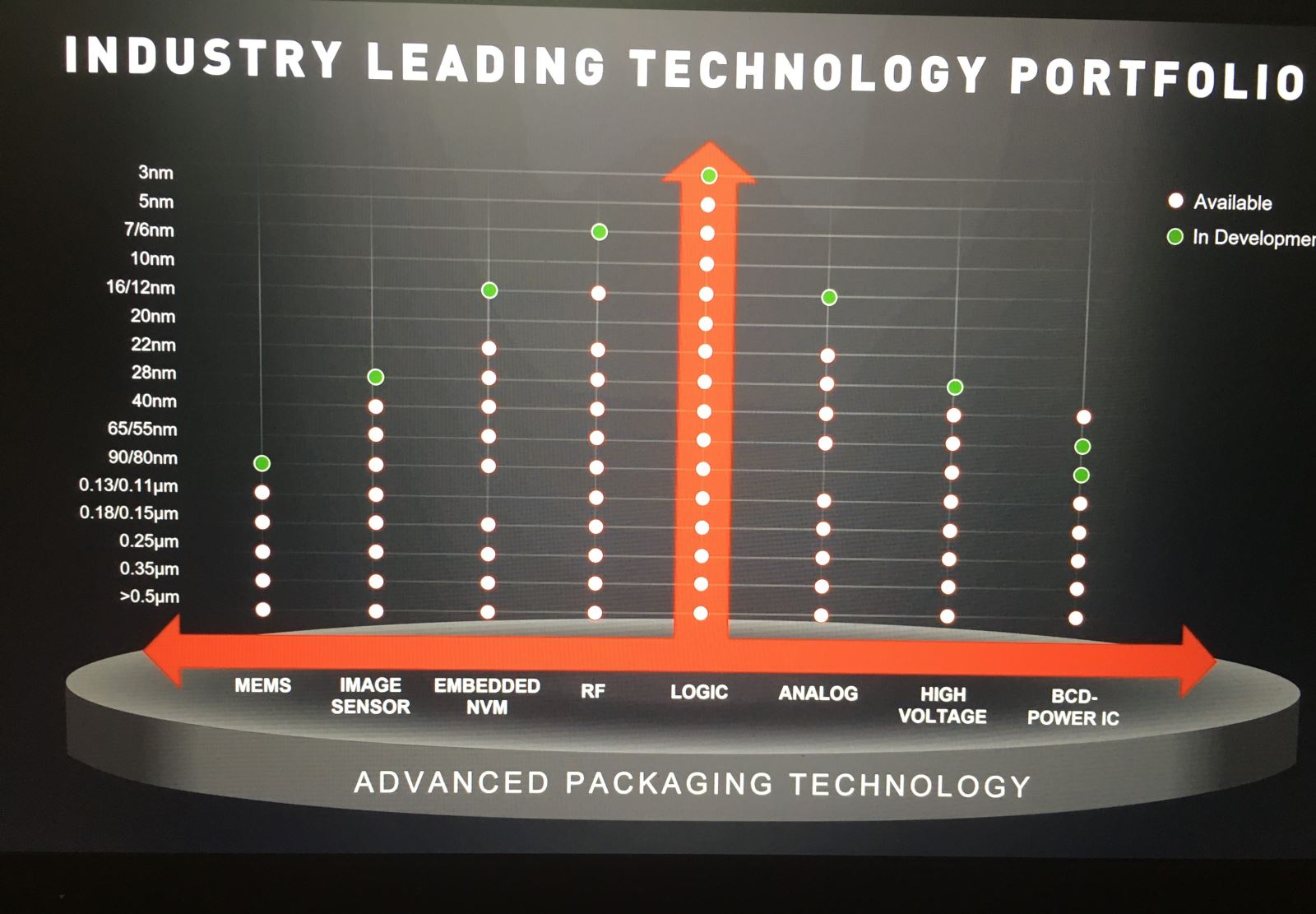

台积公司总裁魏哲家博士在演讲中表示:“COVID-19在全球蔓延,所有行业均面临严峻考验,此刻,人们仰赖科技来彼此沟通、互相打气,我们客户的创新设计让整个世界变得更加智能化、更具连结性,台积公司致力于以最先进的逻辑技术、链接实体与数字世界的特殊工艺组合、先进封装技术、以及完备的系统整合解决方案来协助客户释放创新。”

本次论坛聚焦在先进工艺、特殊工艺、先进封装、卓越制造等四个方面,全面展现了台积公司在这些领域强大的技术实力,并让业界从中了解台积公司的未来发展规划。

图1 台积公司整体技术发展路线图

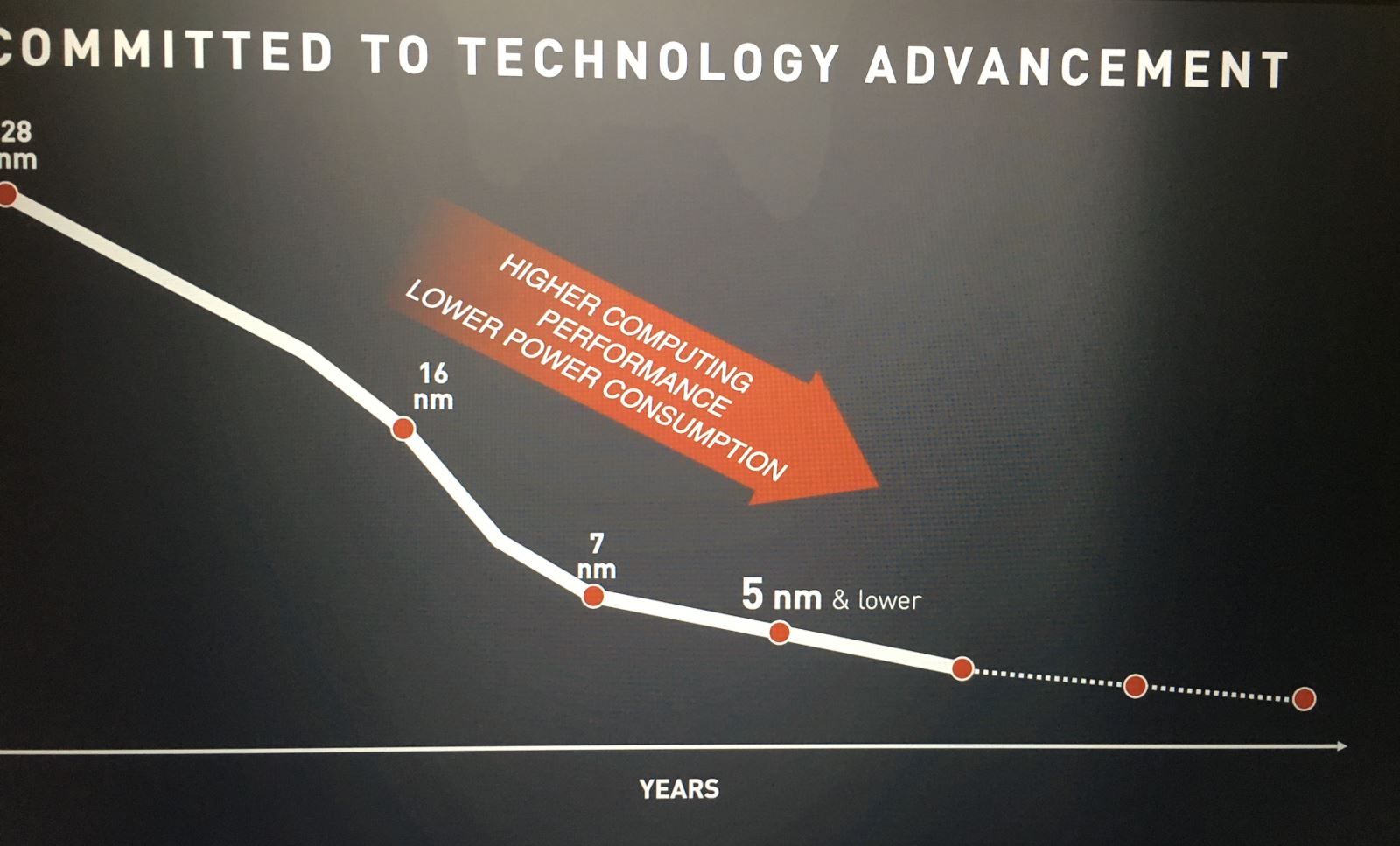

先进技术的领导地位横跨N5、N4、以及N3

台积公司业界领先的N5技术今年已进入量产,随着产能持续拉升,良率提升的速度亦较前一世代技术快。相较于前一世代的N7技术,N5速度增快15%、功耗降低30%、逻辑密度增加达80%。奠基于N5技术,台积公司预计于2021年量产加强版的N5P工艺,速度可再增快5%,功耗再降低10%。

此外,台积公司还揭示了5纳米家族的最新成员-N4工艺,N4进一步提升效能、功耗、以及密度来满足多样化产品的需求,除了减少光罩层来简化工艺,N4可借助5纳米完备的设计生态系统顺利从N5升级,N4工艺预计于2021年第四季开始试产,2022年进入量产。

图2 台积公司在先进工艺上的技术发展路线图

展望下一世代技术,台积公司N3工艺开发进度符合预期,将成为全球最先进的逻辑技术,相较于N5技术,N3速度增快15%,功耗降低达30%,逻辑密度增加达70%。随着半导体架构的创新,台积公司从5纳米往前推进了一个全世代工艺,持续保持技术的领导地位。

支持5G与人工智能时代物联网设备的N12eTM 技术

台积公司拥有的N12e工艺目前已进入试产阶段,该工艺能够提供强大的运算效能与优异的功耗效率,支持人工智能边缘运算应用。N12e将台积公司强大的FinFET晶体管技术导入边缘装置,藉由强化的超低漏电装置与静态随机存取内存,相较于前一世代的22ULL技术,N12e逻辑密度增加超过1.75倍,效能提升约1.5倍,功耗减少一半。做为12FFC+工艺的加强版,N12e适合应用于支持人工智能的物联网装置,提供强大的功能执行力,例如,理解自然语言或影像分类,同时提升功耗效率;N12e也能够支持用电池供电的强大人工智能物联网装置。

3DFabricTM系统整合解决方案

台积公司在本次论坛上隆重介绍的3DFabric,将快速成长的三维集成电路(3DIC)系统整合解决方案统合起来,提供无与伦比的灵活性,透过稳固的芯片互连打造出强大的系统。藉由不同的选项进行前段芯片堆栈与后段封装,3DFabric协助客户将多个逻辑芯片链接在一起,甚至串联高带宽内存(HBM),或异质小芯片,例如模拟、输入/输出、以及射频模块。3DFabric是业界首项能够结合后段3D与前段3D技术的解决方案,提供系统整合中的强大乘数效应;同时,3DFabric能与晶体管微缩互补,持续提升系统效能与功能性,缩小尺寸外观,并且加

快产品上市时程。

3DFabric包含台积公司的系统整合芯片(TSMC-SoICTM)技术、CoWoS®技术、以及整合型扇出(InFO)技术。

截至目前,台积公司的N7技术出货量已经达到10亿颗,而N7+更是业界第一个将EUV制程成功应用到量产中的技术。随着Fab18的投产,N5、N4的量产即将到来,台积公司在引领半导体技术创新方面展现了异常强大的实力。目前看来,这种创新步伐丝毫没有放缓的迹象,而5G、人工智能等新兴应用将是台积公司技术创新的主要推手。